MOS switch circuit design: a practical case study and the influence of PCB routing parasitic inductance

2024-07-12 14:24:35 1328

MOS, as a member of the field effect transistor (FET) family, can act as a switch, which works by regulating the gate voltage to determine the on-off state of the circuit. This feature makes MOS tube widely used in such fields as digital circuit design, power management system and motor drive, showing an irreplaceable value.

According to its structure and working mode, MOS tubes can be divided into enhanced and depleted types, and there are also P channels and N channels, and theoretically there are four combinations. However, in practical applications, enhanced N-channel MOS tube (NMOS) and enhanced P-channel MOS tube are mainly used. Among them, NMOS is more common in practice due to its cost advantages and lower on-resistance, and occupies a dominant position.

Summary of common problems in the switching circuit of MOS tube

1. MOS tube misdirection and gate breakdown damage

The first problem with MOS tubes is that their gate-drain parasitic capacitance (also called Miller capacitance) causes MOS tubes to self-open.

First, what are the causes of MOS tube misdirection and gate breakdown damage?

As shown in the figure below, when the MOS tube suddenly switches from the on-state to the off state, steep dVDS/dt are generated between the source and drain of the MOS tube. The resulting electricity flows through the Miller capacitor and is coupled to the grid, resulting in a voltage drop in the grid resistance, which increases the grid voltage and produces a large voltage spike. The resulting current is: i=Cgd⋅dVDS/dt.

When i⋅Rg > Vgs(th), the MOS tube will self-conduction, for the H-bridge circuit composed of MOS tube, this self-conduction will bring the upper tube and the lower tube at the same time, which may damage one or two MOS tubes. When the peak voltage of the gate exceeds the maximum voltage allowed between the gate sources, the gate oxide layer of the MOS tube will be broken down, resulting in damage.

Second, how to prevent MOS tube misdirection and gate breakdown damage?

1. Select the appropriate grid series resistance.

The gate of the MOS tube is generally connected with a resistor, so what is the role of this grid series resistance?

The first function is to limit the drive current and prevent the excessive instantaneous drive current from causing insufficient or damaged drive capability of the driver chip. The opening of the MOS tube can be regarded as the charging process of Cgs and Cgd. The charging instantaneous capacitance is equivalent to a short circuit, and the current is very large. The driver chip may not be able to provide such a large current immediately or may be damaged due to excessive current, so a resistance is connected in series to play a role of current limiting and protection.

The second function is to solve the problem mentioned above - to prevent misdirection and gate breakdown damage of the MOS tube. Increasing the gate series resistance of the MOS tube can reduce the on-speed of the switch, thereby reducing dVDS/dt, and then reducing the peak voltage of the gate, so as to prevent the misdirection of the MOS tube and the breakdown damage of the gate oxide layer.

However, the gate resistance of MOS tube is too large, which will reduce the switching speed, lead to increased power loss, and cause potential heating problems. On the contrary, a smaller grid series resistance will increase the switching speed and easily cause voltage spikes. Therefore, the influence of switching speed and peak voltage should be balanced in the selection of gate resistance.

2. Series suitable grid-source capacitors. A capacitor is inserted between the gate and the source, which absorbs the gate-drain current due to dVDS/dt, thereby preventing misdirection of the MOS tube and gate breakdown damage.

3. A TVS diode (transient voltage suppression diode) can be connected in parallel between the grid source, but the appropriate clamping voltage (Vc) needs to be selected. TVS (TRANSIENTVOLTAGE SUPPRESSOR) diode is a kind of overvoltage suppression protection element, also known as ESD (electrostatic protection) diode. TVS diode is generally in reverse parallel with both ends of the protected element, normal operation, the diode is in the cut-off state, does not affect the normal operation of the circuit; However, when there is a transient high voltage shock in the circuit, the diode can quickly reverse breakdown on (the turn-on time is mostly P seconds), and the voltage at both ends of the protected element is clamped at a lower level, so that the protected element is free from damage. The principle of TVS diode protection element is shown in the following figure:

Previously written an article "TVS diode in PCB layout key role and selection";, the TVS diode working principle, parameter selection and so on are introduced in detail, interested can spend two minutes to review.

Previously written an article "TVS diode in PCB layout key role and selection";, the TVS diode working principle, parameter selection and so on are introduced in detail, interested can spend two minutes to review.

② The voltage rings

First, what are the reasons for the MOS tube output voltage ringing?

Voltage ringing is actually the phenomenon of voltage oscillation in the circuit caused by the presence of parameters such as parasitic capacitance and parasitic inductance when the MOS tube switches from one state to another. The voltage ringing phenomenon can be seen at both the input and output ends of the MOS tube, and they will be coupled to each other through the parasitic capacitance of the MOS tube.

A series resonant circuit composed of RLC can be used to intuitively understand the voltage ringing phenomenon of MOS tube. In a series resonant circuit composed of RLC, the resistance R plays a damping role to prevent oscillation, so the larger the R is, the less likely it is to oscillate.

The damping ratio is calculated as follows:

When the damping ratio of ζ is < 1, it belongs to the underdamped state, and the circuit will oscillate.

When the damping ratio ζ=1, it belongs to the critical damping state, and the circuit will not oscillate obviously.

When the damping ratio of ζ is greater than 1, it belongs to the overdamped state, and the step response speed of the circuit becomes slower. The figure for different damping ratios is shown in the figure below.

The RLC series resonant circuit as shown in the figure below is composed of gate resistance, parasitic inductance and gate-source parasitic capacitance of MOS tube switching circuit.

The RLC series resonant circuit as shown in the figure below is composed of gate resistance, parasitic inductance and gate-source parasitic capacitance of MOS tube switching circuit.

Second, the method of reducing voltage ringing

Second, the method of reducing voltage ringing

According to the above analysis of the cause of voltage oscillation, it can be seen that in order to avoid the voltage oscillation of the MOS tube when the switching state is switched, it is only necessary to make the damping ratio > ζ. Therefore, it can be considered from the direction of increasing the series resistance of the grid, reducing the parasitic inductance, and inserting small capacitors between the grid source.

In fact, the above two problems can also be boiled down to one problem, and often occur at the same time, you can use the peak voltage as the first voltage of the ringing, the reason why it is separate, because I think it may be easier to understand. Through the above analysis, we find that the solution is inseparable from the grid series resistance, parasitic inductance, parasitic capacitance. All the above are theoretical analysis. In order to enable everyone to have a more intuitive understanding, INFINITECH will conduct a simple simulation respectively for these three different parameters.

③ Simulation + real case analysis

1. Simulation analysis of the influence of grid series resistance. The gate resistance is equal to 0.1Ω, 100Ω and 1000Ω, and other parameters are consistent, and the gate voltage of the MOS tube is tested during the switching process.

2. Influence of parasitic inductance of grid. Let the parasitic inductance of the gate L1=10nH, L2=100nH and L3=500nH, and keep the other parameters consistent to see how it affects the peak voltage.

2. Influence of parasitic inductance of grid. Let the parasitic inductance of the gate L1=10nH, L2=100nH and L3=500nH, and keep the other parameters consistent to see how it affects the peak voltage.

L parasitic inductors are less visible, but often more important. Let's take a look at a real case of failure caused by ignoring the parasitic inductance of PCB wiring:

L parasitic inductors are less visible, but often more important. Let's take a look at a real case of failure caused by ignoring the parasitic inductance of PCB wiring:

A project needs to be restructured, so the PCB was remade, and after the printed board was welded, the test found that the gate voltage had a large oscillation. As shown in the following picture.

This is clearly a control scheme that has been done, and the devices are the same, why will the grid voltage oscillation occur after the re-fabrication of the board? Through the investigation, carefully the difference between before and after the specific gravity system, it was found that when the designer drew the PCB board, the distance between the MOS tube driver chip and the MOS tube was much farther. This is a real case where the distributed inductance of PCB wiring causes problems.

This is clearly a control scheme that has been done, and the devices are the same, why will the grid voltage oscillation occur after the re-fabrication of the board? Through the investigation, carefully the difference between before and after the specific gravity system, it was found that when the designer drew the PCB board, the distance between the MOS tube driver chip and the MOS tube was much farther. This is a real case where the distributed inductance of PCB wiring causes problems.

Therefore, we must not think that this distributed inductance is very small, so as to ignore its existence. Many times, it is the consideration of these details that determines the level of a hardware engineer.

Of course, the problems caused by these details are also more difficult to troubleshoot, such as the voltage oscillation in this problem may not damage the MOS tube, but it is easy to increase electromagnetic interference (EMI), once the interference is introduced into the system, due to the influence of more factors, it will make the investigation more difficult. In the layout, the drive part must be close to the MOS tube and the drive loop area of the MOS tube should be as short as possible to reduce the influence of parasitic inductance.

④PCB routing parasitic inductance

Many people may not have an intuitive understanding of how large the parasitic inductance of PCB wiring is, perhaps the only understanding is that it is small, which is small in the end? Let's take a look:

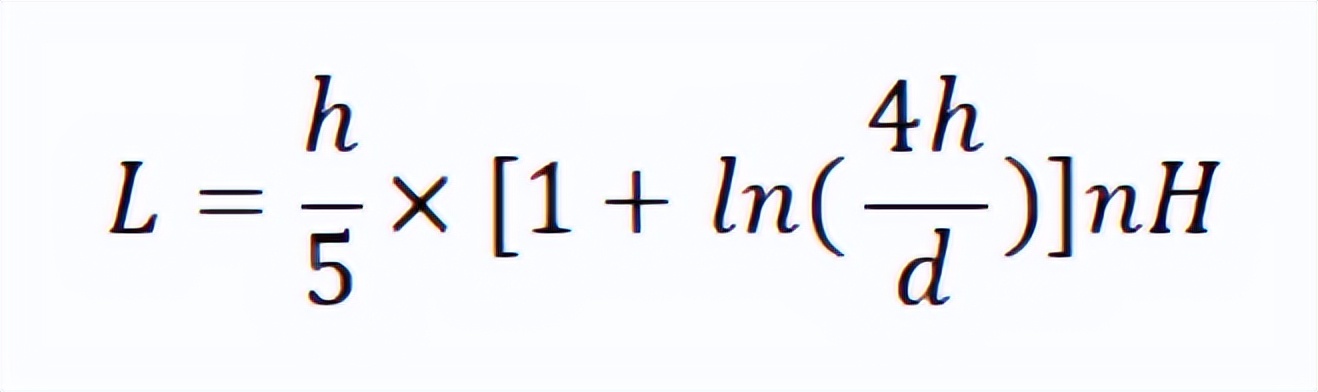

The formula for calculating the inductance of a line on the PCB is:

Where, m is the length of the wire; W is the width of the wire; H is the thickness of the wire.

Where, m is the length of the wire; W is the width of the wire; H is the thickness of the wire.

For example, the inductance of a line on the PCB varies between 6 and 12nH per centimeter.

When drawing multi-layer boards, we inevitably need to use through holes due to wiring constraints, then this through hole will also form a distributed inductance. The formula for calculating the distributed inductance through the hole is as follows:

For example, when a 0.4mm(about 15mil) diameter through the hole through the 15mm thickness of the PCB, there is 1.1nH inductance.

For example, when a 0.4mm(about 15mil) diameter through the hole through the 15mm thickness of the PCB, there is 1.1nH inductance.